Mikroblind- und vergrabene Vias für ultrafeine Schaltkreise

Mikroblind- und vergrabene Vias für ultrafeine Schaltkreise

Maximiert Platzersparnis und Funktionsdichte

Maximiert Platzersparnis und Funktionsdichte

Ermöglicht eine bessere Signalintegrität mit kürzeren Verbindungen

Ermöglicht eine bessere Signalintegrität mit kürzeren Verbindungen

Unterstützt höhere Lagenzahlen in dünneren, leichteren Platinenstrukturen

Unterstützt höhere Lagenzahlen in dünneren, leichteren Platinenstrukturen

Wird in Smartphones, Tablets und tragbarer Elektronik verwendet

Wird in Smartphones, Tablets und tragbarer Elektronik verwendet

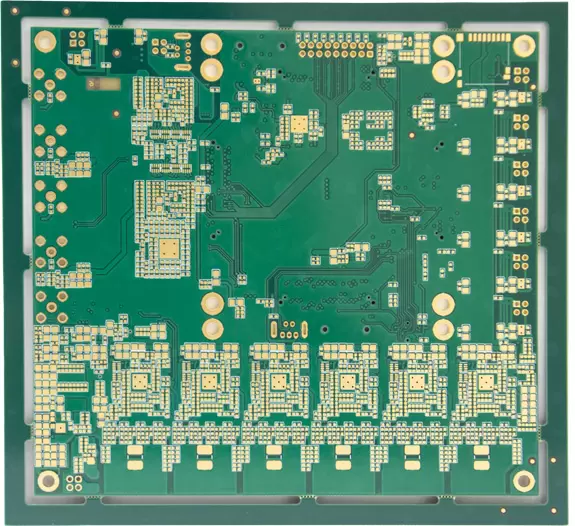

| Besonderheit | Technische Daten |

| Anzahl der Schichten | 4 – 24 Schichten Standard, 40 Schichten Advanced, 60 Schichten Prototyp |

| HDI-Builds | 3+N+3, 4+N+4, jede Ebene in F&E |

| Leiterplattendicke | 0,40 mm – 6,0 mm |

| Kupfergewichte (fertig) | 0,5 OZ – 6 OZ |

| Materialien | Hochleistungs-FR4, halogenfreies FR4, Rogers |

| Maximale Abmessungen | 546 mm x 662 mm |

| Minimale Spurweite und Lücke | 0,075 mm / 0,075 mm |

| Minimaler mechanischer Bohrer | 0,15 mm |

| Verfügbare Oberflächen | HASL (SnPb), LF HASL (SnNiCu), OSP, ENIG, Chemisch Zinn, Chemisch Silber, Elektrolytgold, Goldfinger |

| Minimun-Laserbohrer | 0,10 mm Standard, 0,075 mm Vorlauf |

| Spezialverfahren | Blinde/vergrabene Vias, Via-in-Pad, Backdrill, Sideplating, Senklöcher |

![]()

Technischer Support

![]()

Prototyping-Dienste

![]()

Schnelle Bearbeitung

![]()

Nahtloser Übergang zur Massenproduktion

Wie wähle ich Materialien für HDI aus?

Wie wähle ich Materialien für HDI aus?  Warum sollte ich auf HDI-Leiterplatten umsteigen?

Warum sollte ich auf HDI-Leiterplatten umsteigen?  Wie hoch ist die Genauigkeit des Laserbohrens?

Wie hoch ist die Genauigkeit des Laserbohrens?  Wie halten HDI-Leiterplatten meine Kosten niedrig?

Wie halten HDI-Leiterplatten meine Kosten niedrig?  Was ist eine HDI-Leiterplatte?

Was ist eine HDI-Leiterplatte?

Kundendienst